## 6-Channel PWM-Output Fan RPM Controller

## **General Description**

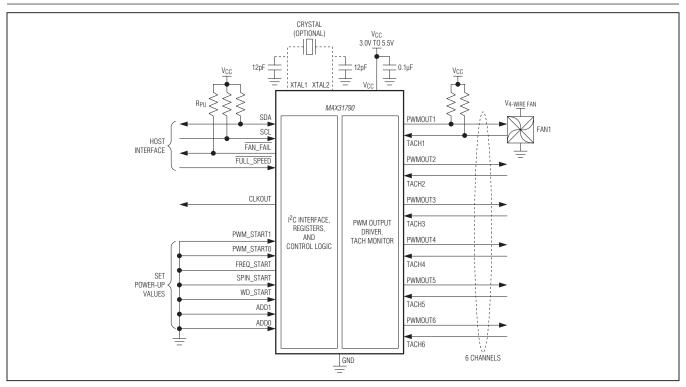

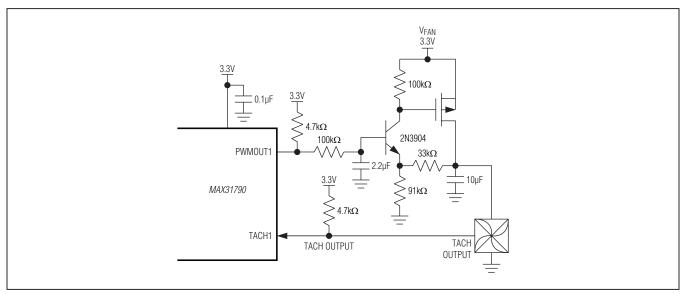

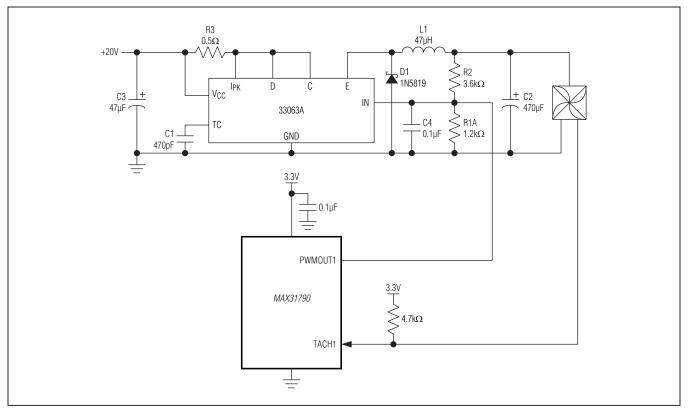

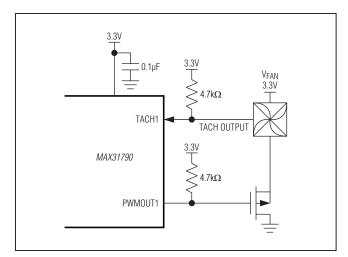

The MAX31790 controls the speeds of up to six fans using six independent PWM outputs. The desired fan speeds (or PWM duty cycles) are written through the I<sup>2</sup>C interface. The outputs drive "4-wire" fans directly, or can be used to modulate the fan's power terminals using an external pass transistor.

Tachometer inputs monitor fan tachometer logic outputs for precise  $(\pm 1\%)$  monitoring and control of fan RPM as well as detection of fan failure. Six pins are dedicated tachometer inputs. Any of the six PWM outputs can also be configured to serve as tachometer inputs.

The PWM\_START inputs select the PWM output status at startup to ensure appropriate fan drive when power is first applied.

To ensure low acoustic impact of fan control, all changes in PWM duty cycle take place at a controlled, programmable rate.

The MAX31790's 3.0V to 5.5V supply voltage range and  $I^2C$ -compatible interface make it ideal for fan control in a wide range of cooling applications. The MAX31790 is available in a 28-pin TQFN package and operates over the -40°C to +125°C temperature range.

## **Features**

- ♦ Controls Up to Six Independent Fans with PWM Drive

- ♦ Up to 12 Tachometer Inputs

- ♦ Controlled Duty Cycle Rate-of-Change for Best Acoustics

- ♦ I<sup>2</sup>C Bus Interface with Timeout and Watchdog

- ♦ 3.0V to 5.5V Supply Voltage Range

- ◆ 1.5mA (typ) Operating Supply Current

## **Applications**

Servers

Networking

Telecom

Ordering Information appears at end of data sheet.

For related parts and recommended products to use with this part, refer to: <a href="https://www.maximintegrated.com/MAX31790.related">www.maximintegrated.com/MAX31790.related</a>

## **Typical Operating Circuit**

# 6-Channel PWM-Output Fan RPM Controller

## **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on V <sub>CC</sub> , SDA, SCL, ADD0, ADD1, FAN_FAIL, PWMOUTn Relative to GND0.3V to +6.0V | Continuous Power Dissipation (T <sub>A</sub> = +70°C) TDFN (derate 20.8 mW/°C above +70°C)1666.7 mW |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Voltage Range on TACHn, WD_START, SPIN_START, FREQ_START, CLKOUT, FULL_SPEED,                           | Operating Temperature Range                                                                         |

| PWM_STARTn Relative to GND0.3V to V <sub>CC</sub> + 0.3V                                                | Junction Temperature+150°C                                                                          |

| (not to exceed +6.0V)                                                                                   | ESD Protection (All Pins, HBM) (Note 1) ±2000V                                                      |

| Input Current at Any Pin+5mA Package Input Current+20mA                                                 | Lead Temperature (soldering, 10s) +300°C<br>Soldering Temperature (reflow) +260°C                   |

**Note 1:** Human Body Model, 100pF discharged through a  $1.5k\Omega$  resistor.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## RECOMMENDED OPERATING CONDITIONS

$(T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ unless otherwise noted.})$  (Notes 2, 3)

| PARAMETER                | SYMBOL          | CONDITIONS | MIN                   | TYP | MAX                   | UNITS |

|--------------------------|-----------------|------------|-----------------------|-----|-----------------------|-------|

| Operating Supply Voltage | V <sub>CC</sub> |            | 3.0                   | 3.3 | 5.5                   | V     |

| Input High Voltage       | V <sub>IH</sub> |            | V <sub>CC</sub> × 0.7 |     |                       | V     |

| Input Low Voltage        | V <sub>IL</sub> |            |                       |     | V <sub>CC</sub> x 0.3 | V     |

## **ELECTRICAL CHARACTERISTICS**

$(T_A = -40^{\circ}\text{C to } + 125^{\circ}\text{C}, \text{ typical values are } V_{CC} = 3.3\text{V}, T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Notes 2, 3)

| PARAMETER                                           | SYMBOL           | CONDITIONS                                    | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------------|------------------|-----------------------------------------------|------|------|------|-------|

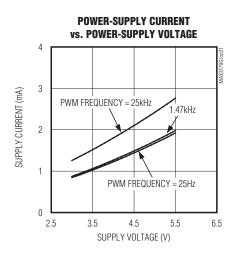

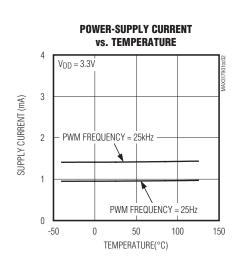

| Quiescent Supply Current                            | laa              | 3.0V < V <sub>CC</sub> < 3.6V                 |      | 1.5  | 3    | mA    |

| (Note 4)                                            | lcc              | 4.5V < V <sub>CC</sub> < 5.5V                 |      | 2.5  | 8    | IIIA  |

| POR Threshold                                       | V <sub>POR</sub> |                                               |      | 2    |      | V     |

| Watchdog Timer Accuracy                             |                  | f <sub>TOSC</sub> = 32.768kHz (Note 5)        | -0.5 |      | +0.5 | S     |

| Output Low Voltage (SDA, FAN_FAIL, PWMOUTn, CLKOUT) |                  | I <sub>OL</sub> = 3mA                         |      |      | 0.4  | V     |

| Output High Voltage (CLKOUT)                        |                  | $I_{OH} = 1 \text{mA}, V_{CC} = 3.0 \text{V}$ | 2.7  |      |      | V     |

| XTAL1 Input Threshold                               |                  |                                               |      | 0.85 |      | V     |

| Input Leakage                                       | ΙL               | (Note 6)                                      | -1   |      | +1   | μΑ    |

| Input Capacitance                                   |                  | All digital inputs                            |      | 5    |      | рF    |

## **FAN CONTROL CHARACTERISTICS**

$(T_A = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ typical values are } V_{CC} = 3.3V, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$  (Note 3)

| PARAMETER                                          | SYMBOL            | CONDITIONS                                                                                                                                      | MIN  | TYP    | MAX  | UNITS |

|----------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|------|-------|

| PWM Resolution                                     |                   |                                                                                                                                                 | 9    |        | 9    | Bits  |

| PWM Frequency Accuracy                             |                   |                                                                                                                                                 | -6   | -      | +6   | %     |

| TACH Count Resolution                              |                   |                                                                                                                                                 | 11   |        | 11   | Bits  |

| TACH Count Oscillator and CLKOUT Clock             | f <sub>TOSC</sub> | (Note 7)                                                                                                                                        |      | 32.768 |      | kHz   |

|                                                    | tenn.toco         | Using internal oscillator:<br>T <sub>A</sub> = +25°C, V <sub>CC</sub> = 3.3V                                                                    | -0.5 |        | +0.5 |       |

| TAGUG                                              |                   | Using internal oscillator:<br>0°C < T <sub>A</sub> < +70°C, 3.0V < V <sub>CC</sub> < 3.6V                                                       | -2.5 |        | +2.5 |       |

| TACH Count Oscillator and CLKOUT Accuracy (Note 7) |                   | Using internal oscillator:<br>-40°C < T <sub>A</sub> < +125°C, 3.0V < V <sub>CC</sub> < 3.6V                                                    | -4.0 |        | +4.0 | %     |

|                                                    |                   | Using internal oscillator: $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +125^{\circ}\text{C}, 3.0\text{V} < \text{V}_{\text{CC}} < 5.5\text{V}$ | -7.0 |        | +7.0 |       |

|                                                    |                   | Using external crystal                                                                                                                          | -0.1 |        | +0.1 |       |

| TACH Minimum Input Pulse<br>Width                  | †TACHMIN          | Pulse width must be greater than this value to be detected                                                                                      | 25   |        | 75   | μs    |

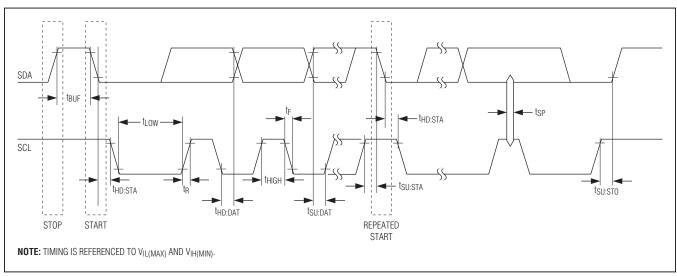

## **12C AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ timing referenced to } V_{IL(MAX)} \text{ and } V_{IH(MIN)}, \text{ unless otherwise noted.})$  (Notes 3, 8) (Figure 1)

| PARAMETER                                       | SYMBOL              | CONDITIONS                        | MIN | TYP         | MAX            | UNITS |

|-------------------------------------------------|---------------------|-----------------------------------|-----|-------------|----------------|-------|

| Serial Clock Frequency                          | f <sub>SCL</sub>    |                                   | DC  |             | 400            | kHz   |

| Bus Free Time Between STOP and START Conditions | t <sub>BUF</sub>    |                                   | 1.3 |             |                | μs    |

| START Condition Hold Time                       | t <sub>HD:STA</sub> |                                   | 0.6 |             |                | μs    |

| STOP Condition Setup Time                       | t <sub>SU:STO</sub> | 90% of SCL to 10% of SDA          | 600 |             |                | ns    |

| Clock Low Period                                | t <sub>LOW</sub>    |                                   | 1.3 |             |                | μs    |

| Clock High Period                               | tHIGH               |                                   | 0.6 |             |                | μs    |

| START Condition Setup Time                      | t <sub>SU:STA</sub> | 90% of SCL to 90% of SDA          | 100 |             |                | ns    |

| Data Setup Time                                 | t <sub>SU:DAT</sub> | 10% of SDA to 10% of SCL          | 100 |             |                | ns    |

| Data In Hold Time                               | t <sub>HD:DAT</sub> | 10% of SCL to 10% of SDA (Note 9) | 0   |             | 0.9            | μs    |

| Maximum Receive SCL/SDA Rise Time               | t <sub>R</sub>      | (Note 10)                         |     | 300         |                | ns    |

| Minimum Receive SCL/SDA Rise Time               | t <sub>R</sub>      | (Note 10)                         | 20  | ) + 0.1 x ( | C <sub>B</sub> | ns    |

## I<sup>2</sup>C AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0V \text{ to } +5.5V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ timing referenced to } V_{IL(MAX)} \text{ and } V_{IH(MIN)}, \text{ unless otherwise noted.})$  (Notes 3, 8) (Figure 1)

| PARAMETER                                  | SYMBOL               | CONDITIONS                              | MIN                             | TYP | MAX | UNITS |

|--------------------------------------------|----------------------|-----------------------------------------|---------------------------------|-----|-----|-------|

| Maximum Receive SCL/SDA Fall Time          | t <sub>F</sub>       | (Note 10)                               |                                 | 300 |     | ns    |

| Minimum Receive SCL/SDA Fall Time          | t <sub>F</sub>       | (Note 10)                               | 20 + 0.1 × C <sub>B</sub>       |     | ns  |       |

| Transmit SDA Fall Time                     | t <sub>F</sub>       | 10pF ≤ C <sub>B</sub> ≤ 400pF (Note 10) | 20 +<br>0.1 x<br>C <sub>B</sub> |     | 250 | ns    |

| Pulse Width of Suppressed Spike            | t <sub>SP</sub>      |                                         |                                 | 35  |     | ns    |

| SDA Time Low for Reset of Serial Interface | <sup>†</sup> TIMEOUT | (Note 11)                               | 25                              |     | 45  | ms    |

- Note 2: All voltages referenced to ground. Currents entering the IC are specified as positive.

- **Note 3:** Limits are 100% production tested at  $T_A = +25^{\circ}$ C and/or  $T_A = +85^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Typical values are not guaranteed.

- **Note 4:** SDA = SCL =  $V_{CC}$ , PWM active with PWM\_FREQUENCY = 25kHz.

- **Note 5:** The watchdog timer is derived from f<sub>TOSC</sub> and the watchdog timer accuracy specifications do not include the oscillator's associated error f<sub>ERR:TOSC</sub>.

- Note 6: Applies to pins SDA, SCL, PWM\_STARTn, WD\_START, FREQ\_START, SPIN\_START, ADDn, TACHn, PWMOUTn, FULL\_SPEED.

- Note 7: f<sub>TOSC</sub> is used to measure fan speed by counting the number of 8192Hz (f<sub>TOSC</sub>/4) clock cycles that take place during a selectable number of tachometer periods.

- Note 8: All timing specifications are guaranteed by design.

- **Note 9:** A master device must provide a hold time of at least 300ns for the SDA signal to bridge the undefined region of SCL's falling edge.

- Note 10:  $C_B$ —total capacitance of one bus line in pF.

- Note 11: Holding the SDA line low for a time greater than t<sub>TIMEOUT</sub> causes the device to reset SDA to the idle state of the serial bus communication (SDA set high).

## **EXTERNAL CRYSTAL PARAMETERS**

(Note 3)

| PARAMETER                       | SYMBOL         | CONDITIONS | MIN | TYP    | MAX | UNITS |

|---------------------------------|----------------|------------|-----|--------|-----|-------|

| Crystal Oscillator Startup Time |                |            |     | 1      |     | S     |

| Nominal Frequency               | f <sub>O</sub> |            |     | 32.768 |     | kHz   |

| Series Resistance               | ESR            |            |     |        | 50  | kΩ    |

| Load Capacitance                | CL             |            |     | 12     |     | pF    |

# 6-Channel PWM-Output Fan RPM Controller

Figure 1. I<sup>2</sup>C Timing Diagram

## **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# **6-Channel PWM-Output Fan RPM Controller**

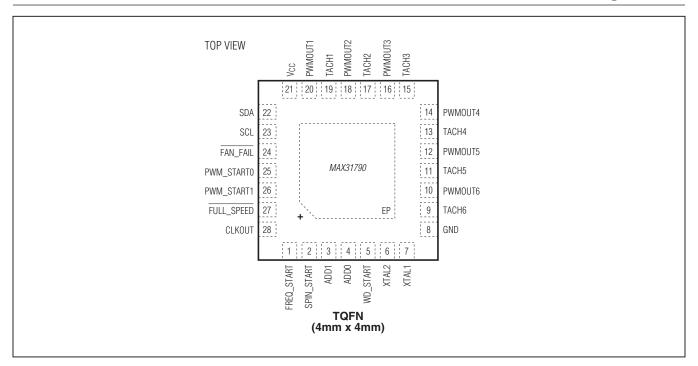

## **Pin Configuration**

## **Pin Description**

| PIN | NAME       | FUNCTION                                                                                                                                                                                                                                                                                     |

|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FREQ_START | This input is sampled at power-up and sets the power-up value for the PWM output frequency. See the <i>Register Map</i> for values.                                                                                                                                                          |

| 2   | SPIN_START | This input is sampled at power-up and sets the initial spin-up behavior. See the <i>Register Map</i> for values.                                                                                                                                                                             |

| 3   | ADD1       | Address Select Inputs. Sampled at the start of every I <sup>2</sup> C transaction. One of 16 possible addresses                                                                                                                                                                              |

| 4   | ADD0       | can be selected by connecting ADD0 and ADD1 to GND, VCC, SDA, or SCL.                                                                                                                                                                                                                        |

| 5   | WD_START   | This input is sampled at power-up and sets the initial I <sup>2</sup> C watchdog behavior. See the <i>Register Map</i> for values.                                                                                                                                                           |

| 6   | XTAL2      | Pins for Connecting to Optional 32,768Hz Crystal. The crystal can be used when the best RPM precision is required. At POR the internal oscillator is used, and a nominal 32,768Hz clock is produced at CLKOUT. If a crystal is connected between XTAL1 and XTAL2, the crystal oscillator can |

| 7   | XTAL1      | be enabled by writing to a register. If no crystal is present, ground XTAL1 and leave XTAL2 unconnected.                                                                                                                                                                                     |

| 8   | GND        | Ground                                                                                                                                                                                                                                                                                       |

# **6-Channel PWM-Output Fan RPM Controller**

## **Pin Description (continued)**

| DIN | NAME       | FUNCTION                                                                                                                                                                                                                                                |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN |            | FUNCTION                                                                                                                                                                                                                                                |

| 9   | TACH6      |                                                                                                                                                                                                                                                         |

| 11  | TACH5      | Logic/Angles Innuts for Tools Cignals If a fee has a logic tools output, it can be used for DDM on                                                                                                                                                      |

| 13  | TACH4      | Logic/Analog Inputs for Tach Signals. If a fan has a logic tach output, it can be used for RPM control. For a 2-wire fan, analog input can be used for fan-failure detection. Also functions as a "locked                                               |

| 15  | TACH3      | rotor" input.                                                                                                                                                                                                                                           |

| 17  | TACH2      | Total input.                                                                                                                                                                                                                                            |

| 19  | TACH1      |                                                                                                                                                                                                                                                         |

| 10  | PWMOUT6    |                                                                                                                                                                                                                                                         |

| 12  | PWMOUT5    |                                                                                                                                                                                                                                                         |

| 14  | PWMOUT4    | Open-Drain Output to 4-Wire Fan's PWM Input or (Less Frequently) to Power Transistor Modulating                                                                                                                                                         |

| 16  | PWMOUT3    | Fan Power Supply. Can also be used as a tachometer signal input. Can be pulled up as high as 5.5V.                                                                                                                                                      |

| 18  | PWMOUT2    |                                                                                                                                                                                                                                                         |

| 20  | PWMOUT1    |                                                                                                                                                                                                                                                         |

| 21  | VCC        | Power-Supply Input. 3.3V nominal. Bypass VCC to GND with a 0.1µF capacitor.                                                                                                                                                                             |

| 22  | SDA        | I <sup>2</sup> C Serial-Data Input/Output, Open Drain. Can be pulled up to 5.5V regardless of VCC.                                                                                                                                                      |

| 23  | SCL        | I <sup>2</sup> C Serial-Clock Input. Can be pulled up to 5.5V regardless of VCC.                                                                                                                                                                        |

| 24  | FAN_FAIL   | Active-Low, Open-Drain Fan-Failure Output. Active only when fault is present.                                                                                                                                                                           |

| 25  | PWM_START0 | These inputs are sampled at power-up and set the power-up value for all PWMOUT duty cycles.                                                                                                                                                             |

| 26  | PWM_START1 | See the Register Map for values.                                                                                                                                                                                                                        |

| 27  | FULL_SPEED | When low, this input forces all PWM outputs to 100%. Exception: If a fan has failed and "Duty Cycle = 0 on Failure" has been selected for that fan.                                                                                                     |

| 28  | CLKOUT     | CMOS Push-Pull 32,768Hz Clock Output. Signal generated from internal oscillator when external crystal is not used. If a crystal is connected between XTAL1 and XTAL2 and enabled, the crystal oscillator generates the output. Output is always active. |

|     | EP         | Exposed Pad. Connect to GND.                                                                                                                                                                                                                            |

# **6-Channel PWM-Output Fan RPM Controller**

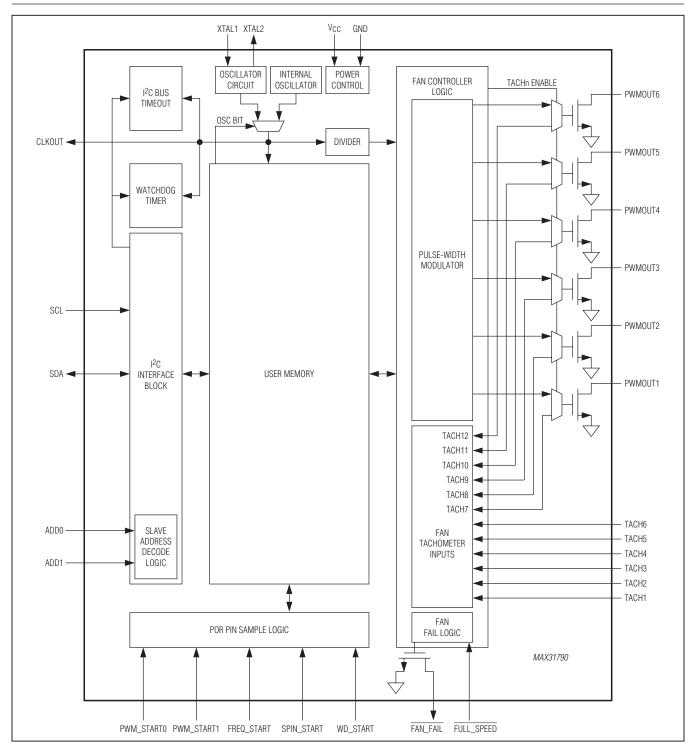

## **Block Diagram**

# 6-Channel PWM-Output Fan RPM Controller

## **Detailed Description**

The MAX31790 controls the speeds of up to six fans using six independent PWM outputs. The desired fan speeds (or PWM duty cycles) are written through the I<sup>2</sup>C interface. The outputs drive "4-wire" fans directly or can be used to control 2-wire or 3-wire fans by modulating the fan's power supply voltage. Modulating the power supply voltage can be achieved by various techniques and are described in the *Controlling 2-Wire and 3-Wire Fans* section.

The MAX31790 has two main methods for controlling fan speeds: PWM mode and RPM mode. Additional level of control is achieved by the incorporated rate-of-change control that allows the device to control the max rate at which the PWM duty cycle is incremented/decremented.

Tachometer inputs monitor fan tachometer logic outputs for precise ( $\pm 1\%$ ) monitoring and control of fan RPM as well as detection of fan failure. Six pins are dedicated tachometer inputs. Any of the six PWM outputs can also be configured to serve as tachometer inputs, allowing for up to 12 fans to be monitored.

The device can monitor the TACHn inputs and determine when a fan has failed. Failure is detected in various ways depending on the fan control mode. Once a selectable number of fault detections has occurred, the FAN\_FAIL output asserts (if fault detection is not masked for the fan).

Power-on values for PWM duty cycles, PWM frequencies, fan spin-up, and the watchdog are achieved by five pin inputs.

#### **Fan Control**

The device has two main methods for controlling fan speeds: PWM mode and RPM mode.

#### **PWM Mode**

In PWM mode, the device produces a PWM waveform that drives the fan's PWM speed control input. The fan's speed is proportional to the PWM duty cycle delivered to its PWM input terminal. The duty cycle is set by the fan's associated PWMOUT Target Duty Cycle registers and the actual duty cycle can be read from the corresponding PWMOUT Duty Cycle register. Because the duty cycle ramps to new values at a controlled rate, the values in the two registers can be different. See the <u>Register Descriptions</u> section for details.

#### RPM Mode

In RPM mode, the device monitors tachometer output pulses from the fan and adjusts the PWM duty cycle to force the fan's speed to the desired value. Fan speed is measured by counting the number of internal 8192Hz (f<sub>TOSC</sub>/4) clock cycles that take place during a selectable number of tachometer periods. The number of clock cycles counted (11-bit value) is stored in the associated TACH Count registers and the desired number of cycles is stored in the TACH Target Count registers. See the *Register Descriptions* section for details.

## Rate-of-Change Control

Sudden changes in fan speed can be easily heard by users. The device helps reduce the audibility of fanspeed changes by controlling the rate at which the PWM duty cycle is incremented. Three bits in the associated Fan Dynamics register sets the rate at which the duty cycle is incremented/decremented. This allows the time required for an LSB of change in the PWM duty cycle to vary from 0ms to 125ms.

The selected rate of change also applies when the FULL\_SPEED input is asserted or when the fans are forced to 100% due to a fan failure. See the <u>Register Descriptions</u> section for details.

In RPM mode when the fan's speed is near the target speed, that is, when the TACH count is near the TACH target count, the control loop dynamics can often be improved by slowing the rate of change of the PWM duty cycle. This operates as follows: First, set a value for the count "window" and store it in the appropriate Window register. In RPM mode, calculate the difference between the current TACH count and the target TACH count. If the absolute value of this difference is less than the value in the appropriate Window register, the update rate of the PWM duty cycle is slowed to 1 LSB per second. When the current TACH count falls outside of the window, the duty cycle rate of change reverts to the selected value.

#### Spin-Up

When a fan is not spinning, and a low duty cycle waveform is applied to its PWM terminal, it can fail to overcome inertia and start spinning. To overcome this potential problem, a 100% duty cycle waveform can be applied to the fan's PWM input for a short time before a lower duty cycle waveform is applied. This "spin-up" period allows the fan to overcome inertia and begin operating. Spin-up is controlled using the corresponding Fan

# 6-Channel PWM-Output Fan RPM Controller

Configuration register. Spin-up can be disabled, or it can cause the fan to be driven with a 100% duty cycle until it produces two tachometer pulses, up to a maximum of 0.5s, 1s, or 2s. When spin-up is enabled and the duty cycle is making a transition from 0% to a value that is less than 100% (from 0% to 50%, for example), the duty cycle first goes to 100%. When two tachometer pulses have been detected, or when the maximum spin-up period has elapsed, the duty cycle drops to the target value (50% in this example). The SPIN\_START pin sets the spin-up value at power-up.

## Sequential Fan Activation

When multiple high-current fans are activated simultaneously, the startup current can stress the system's power supply. To minimize this effect, the device includes a selectable sequential fan activation feature. When selected, this feature inserts a short minimum delay between the activation times of fans.

The bits for controlling sequential fan activation are located in the Failed Fan Options/Sequential Start register. They select the time delay between fan activations to be one of the following: 0, 250ms, 500ms, 1s, 2s, or 4s. The default time is 500ms per channel.

Sequential fan activation applies to POR, fan failure forcing the fans to full speed, and assertion of the FULL\_SPEED input, which forces all the fans to full speed. In all these cases, all fans are forced to full speed. The sequence operates as follows:

- PWM1 activates. The PWM duty cycle begins to increase at the selected rate of change.

- After the selected delay time has elapsed, PWM2 activates. Again, the PWM duty cycle begins to increase at the selected rate of change.

- The other PWM channels activate in sequence, each delayed by the selected delay time relative to the previous channel. Note that the time delay applies to unused or disabled channels.

## FULL\_SPEED Input

Driving this input low forces all fans to full speed with the exception of any failed fans (if 0% on failure has been selected). This input allows an external temperature switch to provide fail-safe overtemperature protection. In systems with multiple MAX31790s, all FAN\_FAIL outputs can be connected to all FULL\_SPEED inputs, thereby providing full-speed operation if any fan fails, regardless

of which MAX31790 controls it. This input is active even in standby mode.

#### **POR Options**

Five inputs allow setup of the device's behavior at powerup. The following inputs are sampled when power is first applied to the device:

**WD\_START:** At power-up the watchdog operation is controlled by the WD\_START pin. Connect WD\_START to V<sub>CC</sub> to enable, or to GND to disable the watchdog function. When enabled using WD\_START, the timeout period is 30s. After power is applied, the watchdog function can be enabled or disabled, and the timeout period can be changed by editing the Global Configuration register.

**SPIN\_START:** At power-up, spin-up operation is controlled by the SPIN\_START pin. Connect SPIN\_START to GND to disable, V<sub>CC</sub> to enable spin-up for a maximum of 1s, or unconnected to enable spin-up for a maximum of 0.5s. After power is applied, the spin-up function can be enabled or disabled, and the spin-up period can be changed by editing the associated Fan Configuration register.

**PWM\_START0, PWM\_START1:** At power-up, the PWM output duty cycles are controlled by the PWM\_START0 and PWM\_START1 pins. Connect PWM\_START0/ PWM\_START1 to GND,  $V_{CC}$ , or leave unconnected to achieve different duty cycles for all PWM outputs. See the PWMOUT Target Duty Cycle register for the corresponding values and connections. After power is applied, the PWM duty cycles can be changed, by editing that PWM's associated PWMOUT Target Duty Cycle register.

**FREQ\_START:** At power-up, all PWM output frequencies are controlled by the FREQ\_START pin. Connect FREQ\_START to GND for 30Hz, V<sub>CC</sub> for 25kHz, or unconnected for 1.47kHz. After power is applied, the PWM output frequencies can be changed by editing the PWM Frequency register.

## Watchdog

The device includes an optional I<sup>2</sup>C watchdog function that monitors the I<sup>2</sup>C bus for transactions. When the watchdog function is enabled, all fans (with the exception of failed fans "0% on fail" selected) are forced to full speed if no I<sup>2</sup>C transactions occur within a selected period (5s, 10s, or 30s). Watchdog timing is selected using the Global Configuration register.

# 6-Channel PWM-Output Fan RPM Controller

## Fan Monitoring

## Monitoring Tachometer Signals

The TACH inputs accept either tachometer or "locked rotor" output signals from 3-wire or 4-wire fans. When measuring fan speed, the device counts the number of internal 8192Hz (f<sub>TOSC</sub>/4)clock cycles that occur during 1, 2, 4, 8, 16, or 32 tachometer periods. (The speed of each fan is measured once per second.) The number of tachometer periods is selectable for each fan by using the appropriate Fan Dynamics register. Tachometer pulses less than t<sub>TACHMIN</sub> in duration are ignored to minimize the effect of noise on the tachometer lines. The TACH count for a given RPM can be obtained from the following equation:

$$TACH Count = \frac{60}{NP \times RPM} \times SR \times 8192$$

where:

NP = number of tachometer pulses per revolution. Most general-purpose brushless DC fans produce two tachometer pulses per revolution.

SR = 1, 2, 4, 8, 16, or 32. This is the number of tachometer periods over which the tachometer clock is counted. See the Speed Range bit information described in the corresponding Fan Dynamics register description.

The tachometer count consists of 11 bits in the TACH Count registers and is available in RPM and PWM modes. In RPM mode, the desired fan count is written to the associated TACH Target Count register. In PWM mode, the desired fan duty cycle is written to the associated PWMOUT Target Duty Cycle register.

Note that the device is intended to be used with 4-wire fans. Modulating a fan's power supply with a PWM waveform, as is sometimes done with 2-wire and 3-wire fans, results in incorrect tachometer counts due to the periodic removal of power from the fan's internal circuitry. Therefore, it is suggested to use PWM mode when interfacing with 2-wire or 3-wire fans.

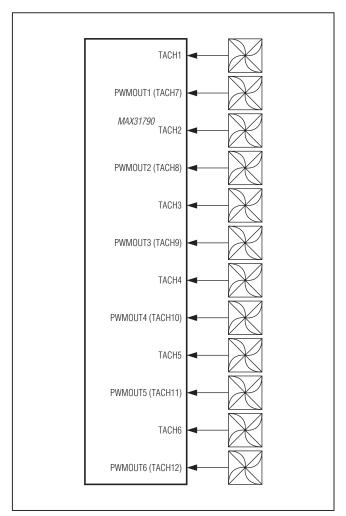

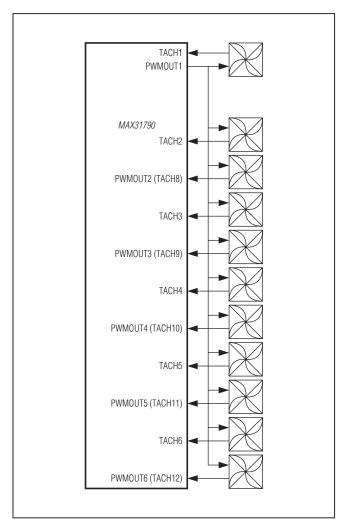

## Using PWM Outputs as Tachometer Inputs

Each Fan Configuration register includes a PWM/TACH bit that allows the PWMOUT to be configured as a TACH input. In TACH mode, the settings for TACH input enable, locked rotor operation, and TACH pulses counted that have been selected for a given fan channel apply to that channel's TACH input and also to TACH signals sensed by that channel's PWM output.

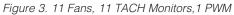

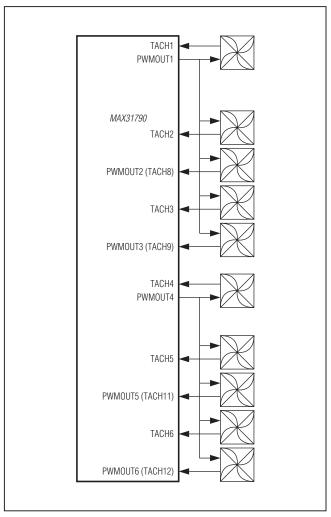

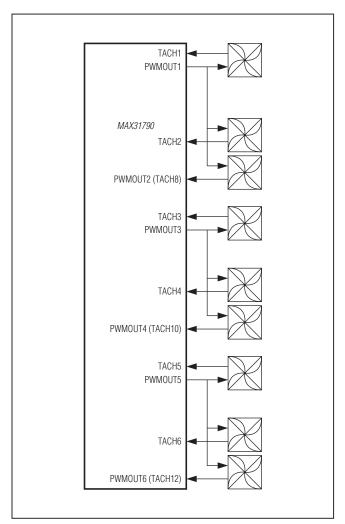

<u>Figure 2</u> to <u>Figure 6</u> show some examples of TACH-PWM connections for various fan configurations

Figure 2. 12 Fans, 12 TACH Monitors, No PWM

# **6-Channel PWM-Output Fan RPM Controller**

Figure 4. 10 Fans, 10 TACH Monitors, 2 PWMs

# 6-Channel PWM-Output Fan RPM Controller

Figure 5. 9 Fans, 9 TACH Monitors, 3 PWMs

# TACH1 PWMOUT1 MAX31790 TACH2 PWMOUT2 (TACH8) TACH3 PWMOUT3 TACH4 PWMOUT4 TACH5 PWMOUT5 (TACH11) TACH6 PWMOUT6

Figure 6. 8 Fans, 8 TACH Monitors, 4 PWMs

#### Fan Failure

When enabled, the device monitors the TACH inputs to determine when a fan has failed. For fans with tachometer outputs, failure is detected in various ways depending on the fan control mode. In every case, from one to six consecutive fault detections (selected by the Fan Fault Queue bits) are required to decide that the fan has failed. When the selected number of fault detections has occurred, the FAN\_FAIL output asserts (if fault detection is not masked for the fan).

#### PWM Mode Failure Detection

In PWM mode, the TACH Target Count register holds the upper limit for tachometer count values. A potential fault condition is identified when the TACH count exceeds the value written to the TACH Target Count register. If the Fan Fault Queue bit value is 1 and the following tachometer count (1 second later) also exceeds the limit value, the fan is considered to have failed. A higher Fan Fault Queue bit value requires a larger number of consecutive values in excess of the limit value. When a PWM output is used as a TACH input, the PWM-mode failure criteria apply. In PWM mode, fan-failure detection is masked when the target duty cycle is set to zero.

#### RPM Mode Failure Detection

In RPM mode, a potential fault condition is identified when any of the following three conditions occur: 1) the TACH count exceeds the associated value stored in the TACH Target Count register while the PWM duty cycle is 100%, 2) the TACH count exceeds two times the TACH Target Count register value while the duty cycle is less than 100%, or 3) the TACH count reaches its maximum value of 7FFh. If the Fan Fault Queue bit value is 1 and the TACH Count value also exceeds the limit value, the fan is considered to have failed. A higher Fan Fault Queue value requires a larger number of consecutive values in excess of the limit value. In RPM mode, fanfailure detection is masked when the TACH Target Count register is set to full scale.

#### Locked Rotor Mode Failure Detection

Some fans have a locked rotor output that produces a logic-level output to indicate that the fan has stopped spinning. Locked rotor signals can be monitored by setting the TACH/Locked Rotor bit in the associated Fan Configuration register. The polarity of the locked rotor signal can be adjusted in this same register. A fan fault is detected when a locked rotor signal has been present for 1 second.

#### Failure Indication

Fan failure is indicated in the Fan Fault register and also with the open-drain FAN\_FAIL output after the number of consecutive faults selected by the Fan Fault Queue bits have occurred. The FAN\_FAIL output can be masked using the mask bits in the Fan Fault Mask register.

When a fan has failed, PWM to the affected fan can continue as though the fan is still operational, or the duty cycle can be automatically set to 0 or 100% as determined by the Failed Fan Options bits. See the <u>Register Descriptions</u> section for full details.

The failed condition can be cancelled by writing PWM Target duty cycle or TACH target count to the fan's control registers. The new value can be the same as the value already in the register. After writing to the register, the fan-failure detection process begins again. If the fan is still in a failed state, fan failure again is detected.

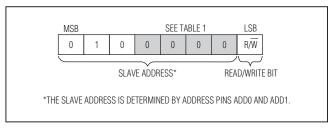

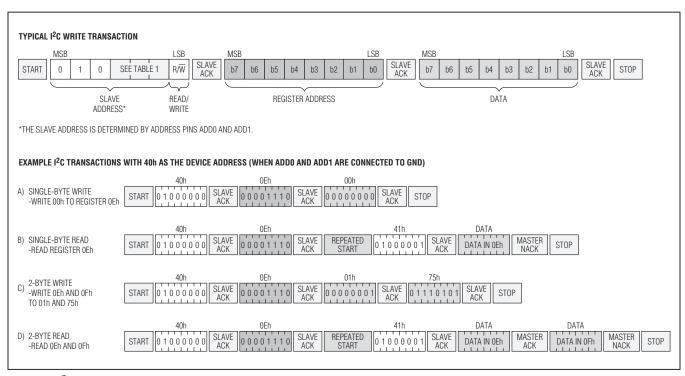

#### **Slave Address Byte and Address Pins**

The slave address byte consists of a 7-bit slave address plus an  $R\overline{W}$  bit (Figure 7). The device's slave address is determined by the state of the ADD0 and ADD1 address pins during a START condition of an I<sup>2</sup>C transaction. The ADD0 and ADD1 pins can be connected to GND, V<sub>CC</sub>, SDA, or SCL. These pins allow up to 16 MAX31790s to

reside on the same I<sup>2</sup>C bus. See <u>Table 1</u> for a complete list of all 16 possibilities and the corresponding ADD0 and ADD1 pin connections.

For example, the device's slave address byte is 40h when ADD0 and ADD1 pins are grounded during a START condition. I<sup>2</sup>C communication is described in detail in the I<sup>2</sup>C Serial Interface Description section.

Note: If the state of the ADD0 and ADD1 pins is changing during normal operation, the slave address of the device dynamically changes to reflect the pins states at every START condition. The ADD0 and ADD1 pins cannot change during an I<sup>2</sup>C transaction.

**Table 1. Slave Address Table**

| ADD1<br>CONNECTION | ADD0<br>CONNECTION | SLAVE<br>ADDRESS BYTE<br>(HEX) |

|--------------------|--------------------|--------------------------------|

| GND                | GND                | 40                             |

| GND                | SCL                | 42                             |

| GND                | SDA                | 44                             |

| GND                | VCC                | 46                             |

| SCL                | GND                | 48                             |

| SCL                | SCL                | 4A                             |

| SCL                | SDA                | 4C                             |

| SCL                | VCC                | 4E                             |

| SDA                | GND                | 50                             |

| SDA                | SCL                | 52                             |

| SDA                | SDA                | 54                             |

| SDA                | VCC                | 56                             |

| VCC                | GND                | 58                             |

| VCC                | SCL                | 5A                             |

| VCC                | SDA                | 5C                             |

| VCC                | VCC                | 5E                             |

Figure 7. MAX31790 Slave Address Byte Example

# 6-Channel PWM-Output Fan RPM Controller

## **Memory Description**

The device's control registers are organized in rows of 8 bytes. The I<sup>2</sup>C master can read or write individual bytes, or can read or write multiple bytes. When writing consecutive bytes, all writes are to the same row. When the final byte in the row is reached, the next byte written is the row's first byte. For example, a write that starts with 02h (Fan 1 Configuration) can write to 02h, 03h, 04h, 05h, 06h, and 07h. If writes continue, the next byte written is 00h, and so on.

Consecutive reads are not subject to the single-row limitation. A read can start at any address and can continue through FFh. If reads continue past FFh, they wrap around to 00h.

"User Bytes" are general-purpose R/W bytes. X denotes the input state at POR.

## **Register Map**

| R/W | REGISTER | POR<br>STATE | FUNCTION                | D7                                    | D6                                                                                                                                                                                                                  | D5                      | D4       | D3                                                | D2                                                          | D1                                                                                                                                                   | D0                              |  |

|-----|----------|--------------|-------------------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------|---------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|

| R/W | 00h      | 0010 0XX0b   | Global<br>Configuration | Run/Standby<br>0 = Run<br>1 = Standby | 0 = Nomal                                                                                                                                                                                                           | Bus Timeout 0 = Enabled | RESERVED | OSC: 0 = Internal oscillator 1 = External crystal | 00b = 1<br>01b<br>10b                                       | I <sup>2</sup> C Watchdog:<br>00b = Disabled<br>01b = 5s<br>10b = 10s<br>11b = 30s                                                                   |                                 |  |

| R/W | 01h      | FREQ_START   | PWM<br>Frequency        |                                       | PWM4-PWM6 Frequency:<br>0000b = 25Hz<br>0001b = 30Hz<br>0010b = 35Hz<br>0011b = 100Hz<br>0100b = 125Hz<br>0101b = 149.7Hz<br>0110b = 1.25kHz<br>0111b = 1.47kHz<br>1000b = 3.57kHz<br>1001b = 5kHz<br>1011b = 25kHz |                         |          |                                                   | 0000k 0001k 0010k 0011b 0100b 0101b 0110b 0111b 1000b 1001k | M3 Frequence 0 = 25Hz 0 = 30Hz 0 = 35Hz 1 = 100Hz 1 = 125Hz 1 = 149.7Hz 1 = 1.25kHz 1 = 1.47kHz 2 = 3.57kHz 3 = 5kHz 1 = 12.5kHz 1 = 25kHz 1 = 25kHz | y:                              |  |

| R/W | 02h      | 0XX0 0000b   | Fan 1<br>Configuration  | Mode:<br>0 = PWM<br>1 = RPM           | 0 = PWM 10h - 2 TACH counts 1 - Monitor                                                                                                                                                                             |                         |          |                                                   | TACH/<br>Locked<br>Rotor<br>0 = TACH<br>1 = Locked<br>Rotor | Locked<br>Rotor<br>Polarity<br>0 = Low<br>1 = High                                                                                                   | PWM/TACH<br>0 = PWM<br>1 = TACH |  |

| R/W | 03h      | 0XX0 0000b   | Fan 2<br>Configuration  | Same as Fan 1 Configuration           |                                                                                                                                                                                                                     |                         |          |                                                   |                                                             |                                                                                                                                                      |                                 |  |

| R/W | 04h      | 0XX0 0000b   | Fan 3<br>Configuration  |                                       | Same as Fan 1 Configuration                                                                                                                                                                                         |                         |          |                                                   |                                                             |                                                                                                                                                      |                                 |  |

# **6-Channel PWM-Output Fan RPM Controller**

## Register Map (continued)

| R/W | REGISTER | POR<br>STATE | FUNCTION               | D7 D6 D5 D4 D3 D2 |                                                                               |                           |                           |                           |                          |                                                | D0                       |  |  |

|-----|----------|--------------|------------------------|-------------------|-------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|--------------------------|------------------------------------------------|--------------------------|--|--|

| R/W | 05h      | 0XX0 0000b   | Fan 4<br>Configuration |                   | Same as Fan 1 Configuration                                                   |                           |                           |                           |                          |                                                |                          |  |  |

| R/W | 06h      | 0XX0 0000b   | Fan 5<br>Configuration |                   |                                                                               | :                         | Same as Fan 1 (           | Configuration             | 1                        |                                                |                          |  |  |

| R/W | 07h      | 0XX0 0000b   | Fan 6<br>Configuration |                   |                                                                               | :                         | Same as Fan 1 (           | Configuration             | 1                        |                                                |                          |  |  |

| R/W | 08h      | 0100 1100b   | Fan 1<br>Dynamics      |                   | 010b = 4 (default) 010b = 3.90625ms per LSB 011b = 7.8125ms per LSB (default) |                           |                           |                           |                          | Asymmetric<br>Rate of<br>Change<br>1 = Enabled | RESERVED                 |  |  |

| R/W | 09h      | 0100 1100b   | Fan 2<br>Dynamics      |                   |                                                                               |                           | Same as Fan 1             | Dynamics                  |                          |                                                |                          |  |  |

| R/W | 0Ah      | 0100 1100b   | Fan 3<br>Dynamics      |                   |                                                                               |                           | Same as Fan 1             | Dynamics                  |                          |                                                |                          |  |  |

| R/W | 0Bh      | 0100 1100b   | Fan 4<br>Dynamics      |                   |                                                                               |                           | Same as Fan 1             | Dynamics                  |                          |                                                |                          |  |  |

| R/W | 0Ch      | 0100 1100b   | Fan 5<br>Dynamics      |                   |                                                                               |                           | Same as Fan 1             | Dynamics                  |                          |                                                |                          |  |  |

| R/W | 0Dh      | 0100 1100b   | Fan 6<br>Dynamics      |                   |                                                                               |                           | Same as Fan 1             | Dynamics                  |                          |                                                |                          |  |  |

| R/W | 0Eh      | 0000 0000b   | User Byte              |                   |                                                                               |                           | _                         |                           |                          |                                                |                          |  |  |

| R/W | 0Fh      | 0000 0000b   | User Byte              |                   |                                                                               |                           |                           |                           |                          |                                                |                          |  |  |

| R/W | 10h      | 0000 0000b   | Fan Fault<br>Status 2  | RESERVED          | RESERVED                                                                      | Fan 12 Fault<br>1 = Fault | Fan 11 Fault<br>1 = Fault | Fan 10 Fault<br>1 = Fault | Fan 9 Fault<br>1 = Fault | Fan 8 Fault<br>1 = Fault                       | Fan 7 Fault<br>1 = Fault |  |  |

| R/W | 11h      | 0000 0000b   | Fan Fault<br>Status 1  | RESERVED          | RESERVED IRESERVEDI                                                           |                           |                           |                           |                          |                                                | Fan 1 Fault<br>1 = Fault |  |  |

| R/W | 12h      | 0011 1111b   | Fan Fault<br>Mask 2    | RESERVED          | RESERVED IRESERVEDI                                                           |                           |                           |                           |                          |                                                | Fan 7 Mask<br>1 = Masked |  |  |

| R/W | 13h      | 0011 1111b   | Fan Fault<br>Mask 1    | RESERVED          | RESERVED                                                                      | Fan 6 Mask<br>1 = Masked  | Fan 5 Mask<br>1 = Masked  | Fan 4 Mask<br>1 = Masked  | Fan 3 Mask<br>1 = Masked | Fan 2 Mask<br>1 = Masked                       | Fan 1 Mask<br>1 = Masked |  |  |

# **6-Channel PWM-Output Fan RPM Controller**

## Register Map (continued)

| R/W | REGISTER | POR<br>STATE | FUNCTION                                      | D7                                                                                                                     | D6 | D5       | D4                                                                                                                                                                                               | D3          | D2                                                                            | D1 | D0 |

|-----|----------|--------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------|----|----|

| R/W | 14h      | 0100 0101b   | Failed Fan<br>Options/<br>Sequential<br>Start | Sequential Start Delay<br>000b = 0s<br>001b = 250ms<br>010b = 500ms<br>011b = 1s<br>100b = 2s<br>101b, 110b, 111b = 4s |    | RESERVED | Failed Fan Options  00b = duty cycle =  0% on fail  01b = Continue  PWM or RPM mode  operation on fail.  10b = duty cycle =  100% on fail  11b = All fans to 100%  on any unmasked fan  failure. |             | Fan Faut Queue  00b = 1 fault  01b = 2 faults  10b = 4 faults  11b = 6 faults |    |    |

| R/W | 15h      | 0000 0000b   | User Byte                                     |                                                                                                                        |    |          | _                                                                                                                                                                                                | 1           |                                                                               |    |    |

| R/W | 16h      | 0000 0000b   | User Byte                                     |                                                                                                                        |    |          | _                                                                                                                                                                                                |             |                                                                               |    |    |

| R/W | 17h      | 0000 0000b   | User Byte                                     |                                                                                                                        |    |          | _                                                                                                                                                                                                |             |                                                                               |    |    |

| R   | 18h      | 1111 1111b   | TACH 1<br>Count MSB                           | 210                                                                                                                    | 29 | 28       | 27                                                                                                                                                                                               | 26          | 25                                                                            | 24 | 23 |

| R   | 19h      | 1110 0000b   | TACH 1<br>Count LSB                           | 22                                                                                                                     | 21 | 20       | 0                                                                                                                                                                                                | 0           | 0                                                                             | 0  | 0  |

| R   | 1Ah      | 1111 1111b   | TACH 2<br>Count MSB                           |                                                                                                                        |    |          | Somo oo TAC                                                                                                                                                                                      | L 1 Count   |                                                                               |    |    |

| R   | 1Bh      | 1110 0000b   | TACH 2<br>Count LSB                           | Same as TACH 1 Count                                                                                                   |    |          |                                                                                                                                                                                                  |             |                                                                               |    |    |

| R   | 1Ch      | 1111 1111b   | TACH 3<br>Count MSB                           |                                                                                                                        |    |          | Same as TAC                                                                                                                                                                                      | H 1 Count   |                                                                               |    |    |

| R   | 1Dh      | 1110 0000b   | TACH 3<br>Count LSB                           |                                                                                                                        |    |          | Same as TAC                                                                                                                                                                                      | TT T Count  |                                                                               |    |    |

| R   | 1Eh      | 1111 1111b   | TACH 4<br>Count MSB                           |                                                                                                                        |    |          | Same as TAC                                                                                                                                                                                      | H 1 Count   |                                                                               |    |    |

| R   | 1Fh      | 1110 0000b   | TACH 4<br>Count LSB                           |                                                                                                                        |    |          |                                                                                                                                                                                                  | TT T Godine |                                                                               |    |    |

| R   | 20h      | 1111 1111b   | TACH 5<br>Count MSB                           |                                                                                                                        |    |          | Same as TAC                                                                                                                                                                                      | H 1 Count   |                                                                               |    |    |

| R   | 21h      | 1110 0000b   | TACH 5<br>Count LSB                           |                                                                                                                        |    |          | Jame as IAC                                                                                                                                                                                      | i i Oouiil  |                                                                               |    |    |

| R   | 22h      | 1111 1111b   | TACH 6<br>Count MSB                           |                                                                                                                        |    |          | Same as TAC                                                                                                                                                                                      | H 1 Count   |                                                                               |    |    |

| R   | 23h      | 1110 0000b   | TACH 6<br>Count LSB                           |                                                                                                                        |    |          | Jame as IAC                                                                                                                                                                                      | i i Oount   |                                                                               |    |    |

| R   | 24h      | 1111 1111b   | TACH 7<br>Count MSB                           |                                                                                                                        |    |          | Same as TAC                                                                                                                                                                                      | H 1 Count   |                                                                               |    |    |

| R   | 25h      | 1110 0000b   | TACH 7<br>Count LSB                           |                                                                                                                        |    |          | Carrie as TAC                                                                                                                                                                                    | i i Oount   |                                                                               |    |    |

# **6-Channel PWM-Output Fan RPM Controller**

## Register Map (continued)

|     |          | DOD          |                               |                             |                |    |                |           |                | I              |                |

|-----|----------|--------------|-------------------------------|-----------------------------|----------------|----|----------------|-----------|----------------|----------------|----------------|

| R/W | REGISTER | POR<br>STATE | FUNCTION                      | D7                          | D6             | D5 | D4             | D3        | D2             | D1             | D0             |

| R   | 26h      | 1111 1111b   | TACH 8<br>Count MSB           |                             |                |    | Same as TACI   | H 1 Count |                |                |                |

| R   | 27h      | 1110 0000b   | TACH 8<br>Count LSB           |                             |                |    | Jame as TAO    | T T Count |                |                |                |

| R   | 28h      | 1111 1111b   | TACH 9<br>Count MSB           |                             |                |    | Same as TACI   | L 1 Count |                |                |                |

| R   | 29h      | 1110 0000b   | TACH 9<br>Count LSB           |                             |                |    |                |           |                |                |                |

| R   | 2Ah      | 1111 1111b   | TACH 10<br>Count MSB          |                             |                |    | Como ao TAO    | I 1 Count |                |                |                |

| R   | 2Bh      | 1110 0000b   | TACH 10<br>Count LSB          |                             |                |    | Same as TACI   | H I Count |                |                |                |

| R   | 2Ch      | 1111 1111b   | TACH 11<br>Count MSB          |                             |                |    | Come as TACI   | I 1 Count |                |                |                |

| R   | 2Dh      | 1110 0000b   | TACH 11<br>Count LSB          |                             |                |    | Same as TACI   | H I Count |                |                |                |

| R   | 2Eh      | 1111 1111b   | TACH 12<br>Count MSB          |                             |                |    |                |           |                |                |                |

| R   | 2Fh      | 1110 0000b   | TACH 12<br>Count LSB          | Same as TACH 1 Count        |                |    |                |           |                |                |                |

| R   | 30h      | 0000 0000b   | PWMOUT 1<br>Duty Cycle<br>MSB | 28                          | 2 <sup>7</sup> | 26 | 2 <sup>5</sup> | 24        | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> |

| R   | 31h      | 0000 0000b   | PWMOUT 1<br>Duty Cycle<br>LSB | 20                          | 0              | 0  | 0              | 0         | 0              | 0              | 0              |

| R   | 32h      | 0000 0000b   | PWMOUT 2<br>Duty Cycle<br>MSB |                             |                |    |                |           |                |                |                |

| R   | 33h      | 0000 0000b   | PWMOUT 2<br>Duty Cycle<br>LSB | Same as PWMOUT 1 Duty Cycle |                |    |                |           |                |                |                |

| R   | 34h      | 0000 0000b   | PWMOUT 3<br>Duty Cycle<br>MSB | Same as PWMOUT 1 Duty Cycle |                |    |                |           |                |                |                |

| R   | 35h      | 0000 0000b   | PWMOUT 3<br>Duty Cycle<br>LSB |                             |                |    |                |           |                |                |                |

# **6-Channel PWM-Output Fan RPM Controller**

## Register Map (continued)

|     |          |              |                                     |                | T        |            |                | 1           |          |          |          |

|-----|----------|--------------|-------------------------------------|----------------|----------|------------|----------------|-------------|----------|----------|----------|

| R/W | REGISTER | POR<br>STATE | FUNCTION                            | D7             | D6       | D5         | D4             | D3          | D2       | D1       | D0       |

| R   | 36h      | 0000 0000b   | PWMOUT 4<br>Duty Cycle<br>MSB       |                |          | Sa         | ıme as PWMOU   | T 1 Duty Cy | clo      |          |          |

| R   | 37h      | 0000 0000b   | PWMOUT 4<br>Duty Cycle<br>LSB       |                |          | 36         | THE AS FWINIOU | T T Duty Cy | Cie      |          |          |

| R   | 38h      | 0000 0000b   | PWMOUT 5<br>Duty Cycle<br>MSB       |                |          | So         | amo oo PW/MOLL | T 1 Duty Cv | olo      |          |          |

| R   | 39h      | 0000 0000b   | PWMOUT 5<br>Duty Cycle<br>LSB       |                |          | Sa         | ime as PWMOU   | T T Duty Cy | cie      |          |          |

| R   | 3Ah      | 0000 0000b   | PWMOUT 6<br>Duty Cycle<br>MSB       |                |          | 0-         | DIAMOLI        | T.1 D.1. O. | -1-      |          |          |

| R   | 3Bh      | 0000 0000b   | PWMOUT 6<br>Duty Cycle<br>LSB       |                |          | Sa         | ime as PWMOU   | I 1 Duty Cy | cie      |          |          |

| R   | 3Ch      | 0000 0000b   | RESERVED                            | 0              | 0        | 0          | 0              | 0           | 0        | 0        | 0        |

| R   | 3Dh      | 0000 0000b   | RESERVED                            | 0              | 0        | 0          | 0              | 0           | 0        | 0        | 0        |

| R   | 3Eh      | 0000 0000b   | RESERVED                            | 0              | 0        | 0          | 0              | 0           | 0        | 0        | 0        |

| R   | 3Fh      | 0000 0000b   | RESERVED                            | 0              | 0        | 0          | 0              | 0           | 0        | 0        | 0        |

| R/W | 40h      | PWM_START    | PWMOUT1<br>Target Duty<br>Cycle MSB | 2 <sup>8</sup> | 27       | <u>2</u> 6 | <u>2</u> 5     | 24          | 23       | 22       | 21       |

| R/W | 41h      | PWM_START    | PWMOUT1<br>Target Duty<br>Cycle LSB | 20             | RESERVED | RESERVED   | RESERVED       | RESERVED    | RESERVED | RESERVED | RESERVED |

| R/W | 42h      | PWM_START    | PWMOUT2<br>Target Duty<br>Cycle MSB |                |          | Como       | oo DMMAOLIT 1  | Toront Duty | Cuala    |          |          |

| R/W | 43h      | PWM_START    | PWMOUT2<br>Target Duty<br>Cycle LSB |                |          | Same       | as PWMOUT 1    | Target Duty | Cycle    |          |          |

| R/W | 44h      | PWM_START    | PWMOUT3<br>Target Duty<br>Cycle MSB |                |          |            |                |             |          |          |          |

| R/W | 45h      | PWM_START    | PWMOUT3<br>Target Duty<br>Cycle LSB |                |          | Same       | as PWMOUT 1    | rarget Duty | Cycle    |          |          |

# **6-Channel PWM-Output Fan RPM Controller**

## Register Map (continued)

|     |          | DOD          |                                     |                                    | 1  |      |                |             | 1        |          |                |

|-----|----------|--------------|-------------------------------------|------------------------------------|----|------|----------------|-------------|----------|----------|----------------|

| R/W | REGISTER | POR<br>STATE | FUNCTION                            | D7                                 | D6 | D5   | D4             | D3          | D2       | D1       | D0             |

| R/W | 46h      | PWM_START    | PWMOUT4<br>Target Duty<br>Cycle MSB |                                    |    | Samo | e as PWMOUT 1  | Target Duty | Cyclo    |          |                |

| R/W | 47h      | PWM_START    | PWMOUT4<br>Target Duty<br>Cycle LSB |                                    |    |      |                |             |          |          |                |

| R/W | 48h      | PWM_START    | PWMOUT5<br>Target Duty<br>Cycle MSB |                                    |    | Come | OS DIMMOLIT 1  | Taxaat Dubu | Cuala    |          |                |

| R/W | 49h      | PWM_START    | PWMOUT5<br>Target Duty<br>Cycle LSB | Same as PWMOUT 1 Target Duty Cycle |    |      |                |             |          |          |                |

| R/W | 4Ah      | PWM_START    | PWMOUT6<br>Target Duty<br>Cycle MSB |                                    |    | 0    | DIMMOLIT       |             | 0 1      |          |                |

| R/W | 4Bh      | PWM_START    | PWMOUT6<br>Target Duty<br>Cycle LSB |                                    |    | Same | e as PWMOUT 1  | Target Duty | Cycle    |          |                |

| R/W | 4Ch      | 0000 0000b   | User Byte                           |                                    |    |      | _              |             |          |          |                |

| R/W | 4Dh      | 0000 0000b   | User Byte                           |                                    |    |      | _              |             |          |          |                |

| R/W | 4Eh      | 0000 0000b   | User Byte                           |                                    |    |      | _              |             |          |          |                |

| R/W | 4Fh      | 0000 0000b   | User Byte                           |                                    |    |      | _              |             |          |          |                |

| R/W | 50h      | 0011 1100b   | TACH 1<br>Target Count<br>MSB       | 2 <sup>10</sup>                    | 29 | 28   | 2 <sup>7</sup> | 26          | 25       | 24       | 2 <sup>3</sup> |

| R/W | 51h      | 0000 0000b   | TACH 1<br>Target Count<br>LSB       | 22                                 | 21 | 20   | RESERVED       | RESERVED    | RESERVED | RESERVED | RESERVED       |

| R/W | 52h      | 0011 1100b   | TACH 2<br>Target Count<br>MSB       |                                    |    |      |                | T 10        |          |          |                |

| R/W | 53h      | 0000 0000b   | TACH 2<br>Target Count<br>LSB       | Same as TACH 1 Target Count        |    |      |                |             |          |          |                |

| R/W | 54h      | 0011 1100b   | TACH 3<br>Target Count<br>MSB       |                                    |    |      |                |             |          |          |                |

| R/W | 55h      | 0000 0000b   | TACH 3<br>Target Count<br>LSB       |                                    |    |      | Same as TACH 1 | rarget Cou  | TIL      |          |                |

# **6-Channel PWM-Output Fan RPM Controller**

## Register Map (continued)

| R/W | REGISTER | POR<br>STATE | FUNCTION                      | <b>D</b> 7       | D6 | D5 | D4             | D3         | D2   | D1 | D0 |

|-----|----------|--------------|-------------------------------|------------------|----|----|----------------|------------|------|----|----|

| R/W | 56h      | 0011 1100b   | TACH 4 Target Count MSB       |                  |    |    | Como oo TACH 1 | Torget Co. | ınt  |    |    |

| R/W | 57h      | 0000 0000b   | TACH 4 Target Count LSB       |                  |    |    | Same as TACH 1 | rarget Cot | arit |    |    |

| R/W | 58h      | 0011 1100b   | TACH 5<br>Target Count<br>MSB |                  |    |    |                | Taxaat Ca  |      |    |    |

| R/W | 59h      | 0000 0000b   | TACH 5<br>Target Count<br>LSB |                  |    | Š  | Same as TACH 1 | rarget Cot | arit |    |    |

| R/W | 5Ah      | 0011 1100b   | TACH 6<br>Target Count<br>MSB |                  |    |    |                | Tayant Cay |      |    |    |

| R/W | 5Bh      | 0000 0000b   | TACH 6 Target Count LSB       |                  |    | Š  | Same as TACH 1 | rarget Cot | arri |    |    |

| R/W | 5Ch      | 0000 0000b   | User Byte                     |                  |    |    |                |            |      |    |    |

| R/W | 5Dh      | 0000 0000b   | User Byte                     |                  |    |    | _              |            |      |    |    |

| R/W | 5Eh      | 0000 0000b   | User Byte                     |                  |    |    |                |            |      |    |    |

| R/W | 5Fh      | 0000 0000b   | User Byte                     |                  |    |    | _              |            |      |    |    |

| R/W | 60h      | 0000 0000b   | Window 1                      | 27               | 26 | 25 | 24             | 23         | 22   | 21 | 20 |

| R/W | 61h      | 0000 0000b   | Window 2                      |                  |    |    | Same as W      | indow 1    |      |    |    |

| R/W | 62h      | 0000 0000b   | Window 3                      |                  |    |    | Same as W      | indow 1    |      |    |    |